pos:

$$111010,100,000$$

$R^{2},yR^{2},x$

$R^{1},yR^{1},x$

$000000000111 07$

$x_{1}^{2} = pos & 07$

$y_{1}^{2} = (pos & 070) >> 3$

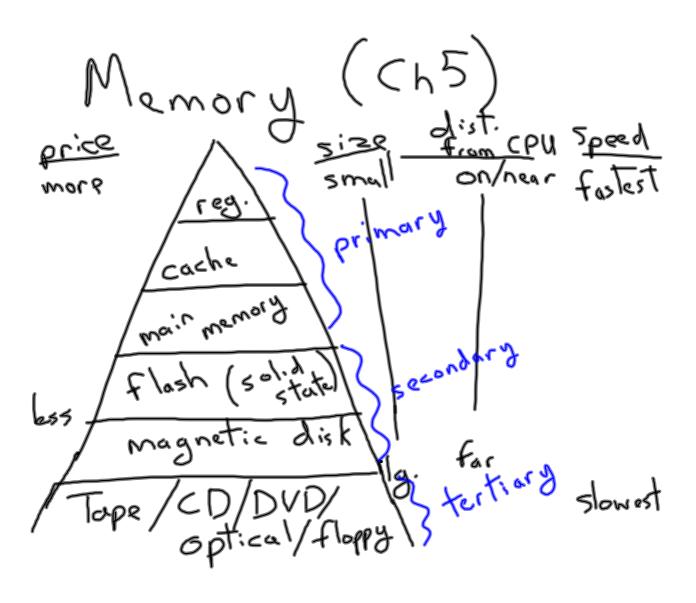

Memory Access

Random

Direct

Sequential

## RAM

Static RAM - flipflops (sram)

Dynamic RAM (DRAM) = | | # -refresh

ROM

Chip

Rom

No

No

No

PROM

ROM

PROM

Ses

EPROM

FLASH

yes (block)

yes

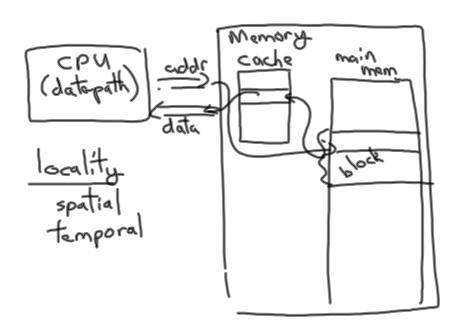

cache hit would the oddr in the cache

-> get block from main memory (put in cache) -> access cache

write policies

write through

write value to main

mem. when changed in

cache

write back

- when block is going

to be replaced

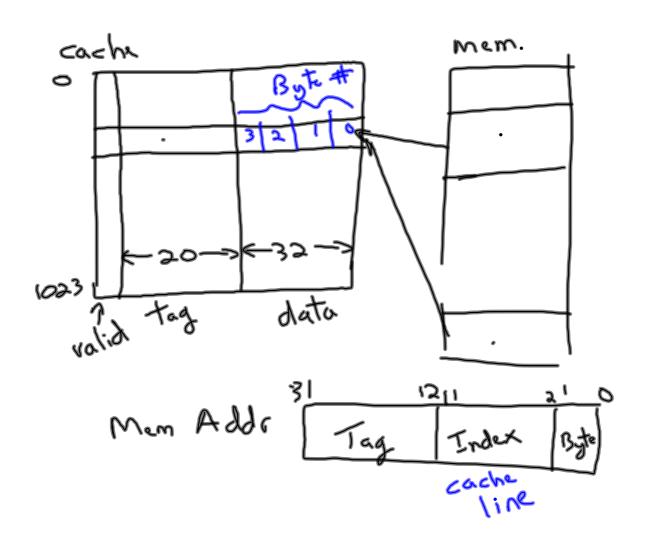

## Direct Mapped Cache

cache index = mem. addr % cache lines

Memory Size: 332 512 lines Cache: Block size: 4 words (16 Bytes) Mem Addr Cache V. Tag rdata

Set-Associative

v tog data v tog data

index